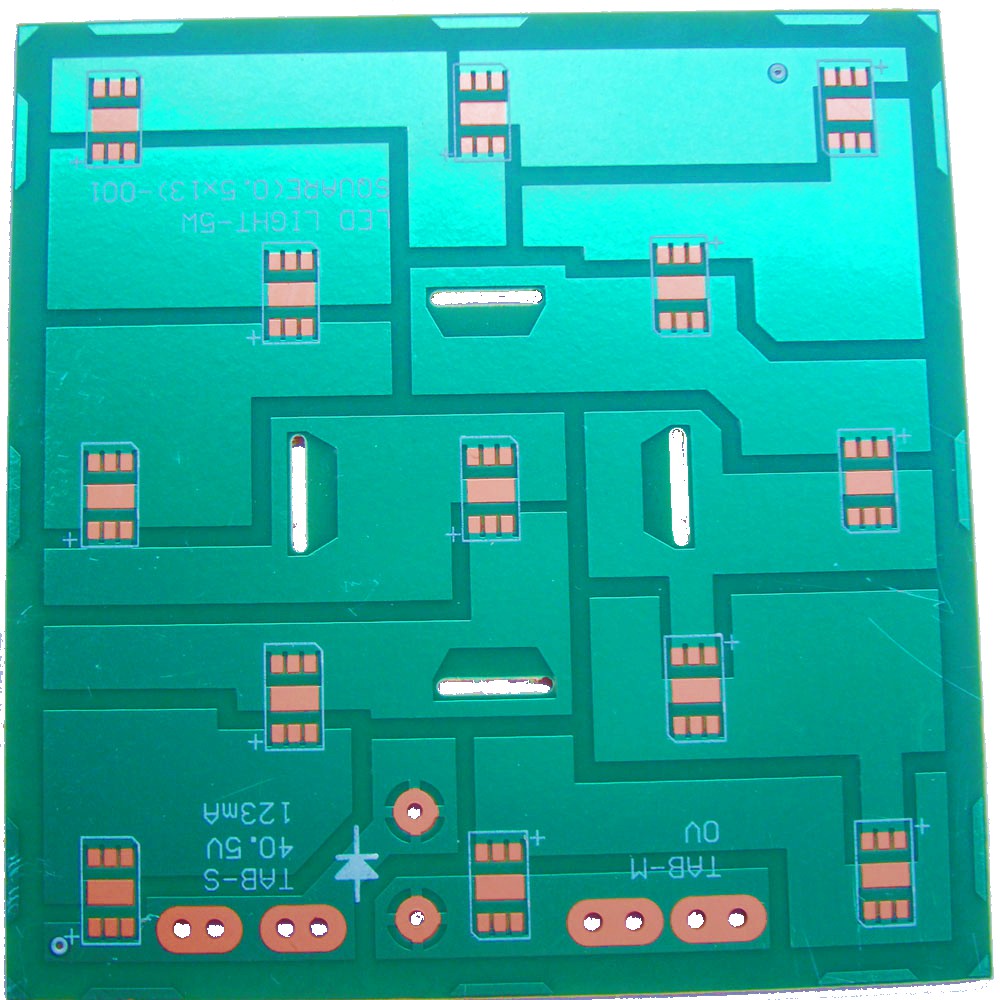

印刷电路板设计中的接地设计

印刷电路板系统设计中最困难的问题之一就是接地设计。虽然它的概念相对简单,但实现起来非常复杂。不幸的是,它没有一种简单的方法可以用详细的步骤来保证良好的结果,但如果一些细节处理不当,可能会导致头痛。

对于线性系统,地面是信号的参考点。遗憾的是,在单极电源系统中,它也被ACTS占用作电源电流的环。如果接地策略应用不当,可能会严重损害高精度线性系统的性能。

接地是所有模拟印刷电路板设计中的一个重要问题,在基于印刷电路板的电路中正确接地也很重要。幸运的是,印刷电路板环境中固有一些高质量的接地原理,尤其是接地层的使用。由于这一因素是基于印刷电路板模拟印刷电路板设计的显著优势之一。

在管理接地的其他方面,包括控制可能导致性能下降的分散接地和信号返回电压。这些电压可能是由外部信号耦合和公共电流引起的,也可能是由接地线中的IR电压下降过大引起的。正确的布线、布线尺寸、差异信号处理和接地隔离技术使我们能够控制这种寄生电压。

事实上,高质量的接地问题必须影响混合信号印刷电路板设计的整体布局原则。

目前的信号处理系统通常需要混合信号设备,如ADC、DAC和快速数字信号处理器。因为需要处理动态范围宽的模拟信号,所以必须使用高性能的ADC和DAC。在恶劣的数字环境中,保持宽动态范围和低噪声与采用良好的高速电路印刷电路板设计技术密切相关,包括适当的信号布线、去耦和接地。

过去,高精度、低速电路被认为不同于所谓的高速电路。对于ADC和DAC,取样(或更新)频率通常用作速度标准。然而,以下两个例子表明,事实上,当今的大多数信号处理技术都是真正的高速,所以它们必须被视为保持高性能的这种设备。DSP、ADC和DAC都是如此。

所有适合信号处理应用的取样ADC(带内置取样保持电路的ADSC)都在快速上升和下降时间(通常为纳秒)的高速时钟上工作,即使吞吐量似乎很低。例如,中速12位接近(SAR)的ADC可以在10MHz的内部时钟上运率只有500kSPS。

σ-δADC采样率高,需要高速钟表。吞吐率范围从10Hz到7.5kHz的高分辨率所谓的低频工业测量ADC(如ad77xx系列)也可以在5MHz以上的钟频率工作,提供24位的分辨率。

更复杂的是,混合信号集成电路具有模拟和数字端口,因此如何使用合适的接地技术变得更加复杂。此外,一些混合信号集成电路的数字电流相对较低,而其他混合信号集成电路的数字电流相对较高。在许多情况下,这两种集成电路需要不同的处理来实现最佳接地。

数字和模拟印刷电路板设计工程师倾向于从不同角度看待混合信号设备。本文的目的是解释适用于大多数混合信号设备的通用接地原理,而不需要了解内部电路的细节。